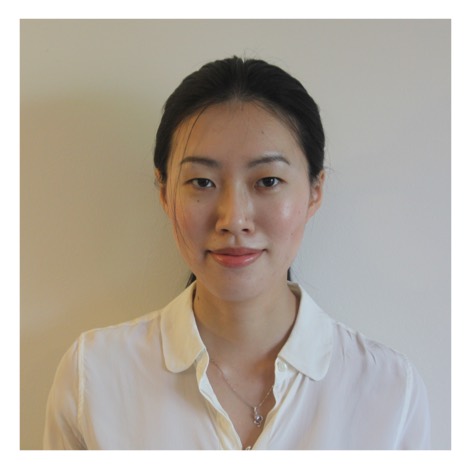

Xiang Ni

PhD Students

xiangni2 at illinois.edu

2173335827

Profile

Xiang Ni is a Ph.D. candidate in the Department of Computer Science at the University of Illinois at Urbana-Champaign. She is interested in developing runtime system techniques for scalable parallel executions on supercomputers. Performance optimization of irregular applications and application oblivious fault tolerance are her primary areas of research. At Illinois, she is part of the Parallel Programming Laboratory which develops Charm++ and its applications. She has closely worked with researchers from Disney Research on developing a first of its kind parallel software for Cloth Simulation. She has also done two summer internships at the Lawrence Livermore National Laboratory. Xiang got her master’s degree at Illinois in 2012 for her work on asynchronous protocols for low overhead checkpointing. Prior to that she got a bachelor’s degree in Computer Science at Beihang University in Beijing, China.

Curriculum Vitae- PDF

Curriculum Vitae- PDF

Research Areas

Papers

17-04

2017

[Paper]

[Paper]

A Memory Heterogeneity-Aware Runtime System for Bandwidth-Sensitive HPC Applications [IPDRM 2017]

16-20

2016

[PhD Thesis]

[PhD Thesis]

Mitigation of failures in high performance computing via runtime techniques [Thesis 2016]

16-15

2016

[Paper]

[Paper]

FlipBack: Automatic Targeted Protection Against Silent Data Corruption [SC 2016]

15-06

2015

[Paper]

[Paper]

Scalable Asynchronous Contact Mechanics using Charm++ [IPDPS 2015]

14-20

2014

[Paper]

[Paper]

Using Migratable Objects to Enhance Fault Tolerance Schemes in Supercomputers [IEEE Transactions on Parallel and Distributed Systems 2014]

14-07

2014

[Paper]

[Paper]

Parallel Programming with Migratable Objects: Charm++ in Practice [SC 2014]

14-04

2014

[Paper]

[Paper]

Maximizing Throughput on a Dragonfly Network [SC 2014]

13-24

2013

[Paper]

[Paper]

ACR: Automatic Checkpoint/Restart for Soft and Hard Error Protection [SC 2013]

12-47

2012

[Paper]

[Paper]

Migratable Objects + Active Messages + Adaptive Runtime = Productivity + Performance: A Submission to the 2012 HPC Class II Challenge [SC 2012]

12-32

2012

[Paper]

[Paper]

Hiding Checkpoint Overhead in HPC Applications with a Semi-Blocking Algorithm [Cluster 2012]

12-15

2012

[MS Thesis]

[MS Thesis]

A Semi-Blocking Checkpoint Protocol to Minimize Checkpoint Overhead [Thesis 2012]

12-14

2012

[Paper]

[Paper]

A Message-Logging Protocol for Multicore Systems [FTXS 2012]

12-12

2012

[Paper]

[Paper]

A Scalable Double In-memory Checkpoint and Restart Scheme towards Exascale [FTXS 2012]

12-04

2012

[Paper]

[Paper]

A Scalable Double In-memory Checkpoint and Restart Scheme towards Exascale [PPL Technical Report 2012]

11-30

2011

[Paper]

[Paper]

Design and Analysis of a Message Logging Protocol for Fault Tolerant Multicore Systems [PPL Technical Report 2011]

Talks/Posters

13-65

2013

[Talk]

[Talk]

ACR: Automatic Checkpoint/Restart for Soft and Hard Error Protection [JLPC 2013]

13-49

2013

[Talk]

[Talk]

ACR: Automatic Checkpoint/Restart for Soft and Hard Error Protection [SC 2013]

13-03

2013

[Poster]

[Poster]

Charm++: Migratable Objects + Active Messages + Adaptive Runtime = Productivity + Performance [PSAAP Site-visit 2013]

12-34

2012

[Talk]

[Talk]

A Scalable Double In-memory Checkpoint and Restart Scheme towards Exascale [FTXS 2012]

12-30

2012

[Talk]

[Talk]

A Message-Logging Protocol for Multicore Systems [FTXS 2012]